地表最强开源gVim编写Verilog插件 |

您所在的位置:网站首页 › gvim linux安装 › 地表最强开源gVim编写Verilog插件 |

地表最强开源gVim编写Verilog插件

|

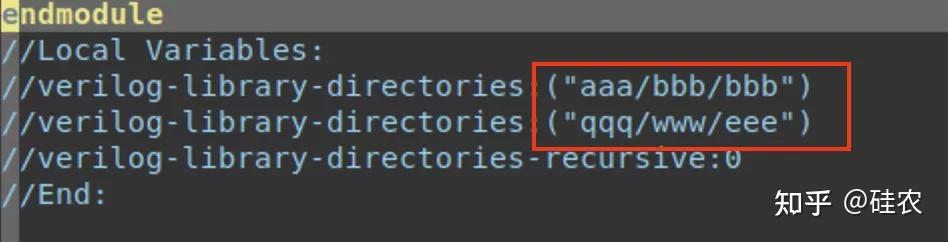

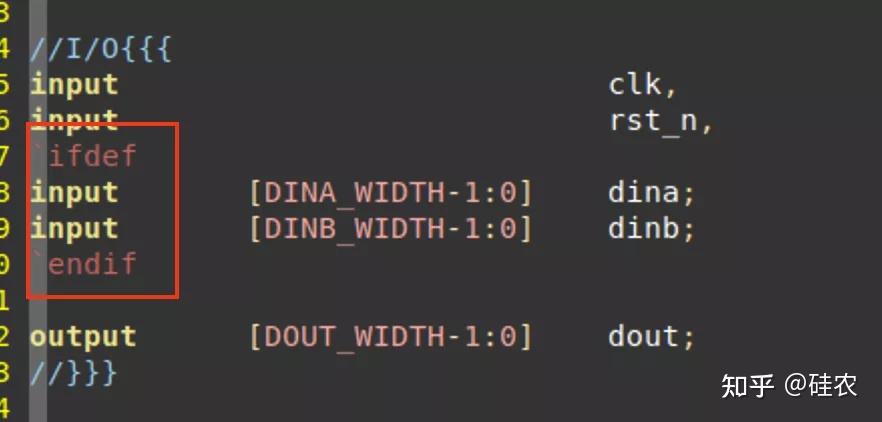

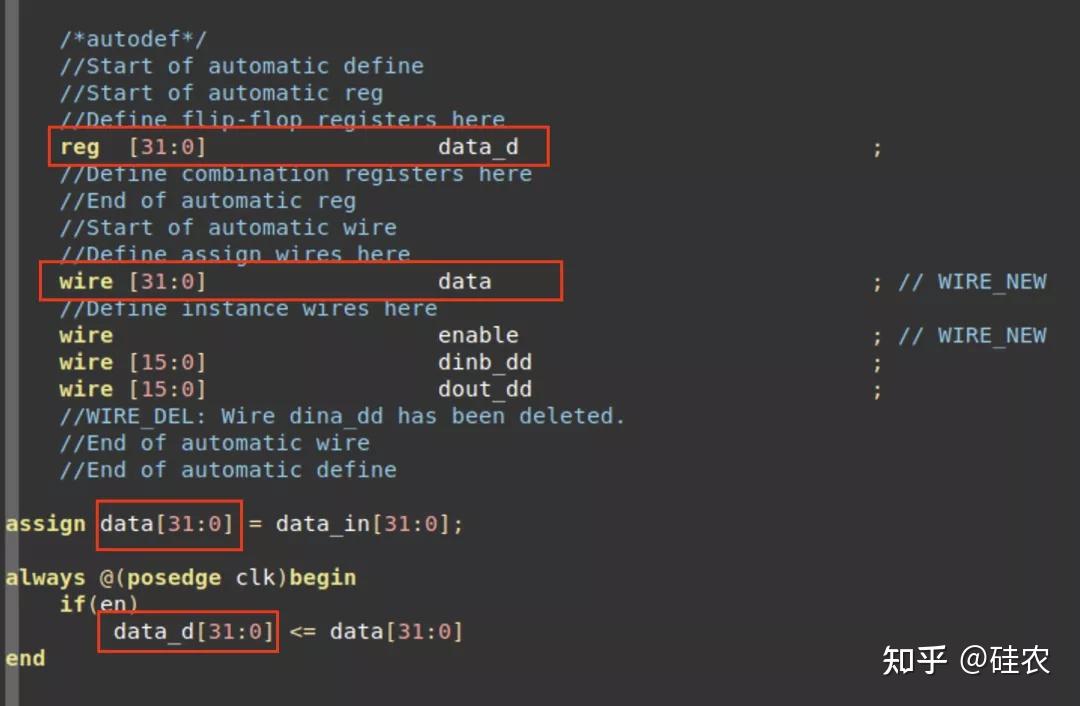

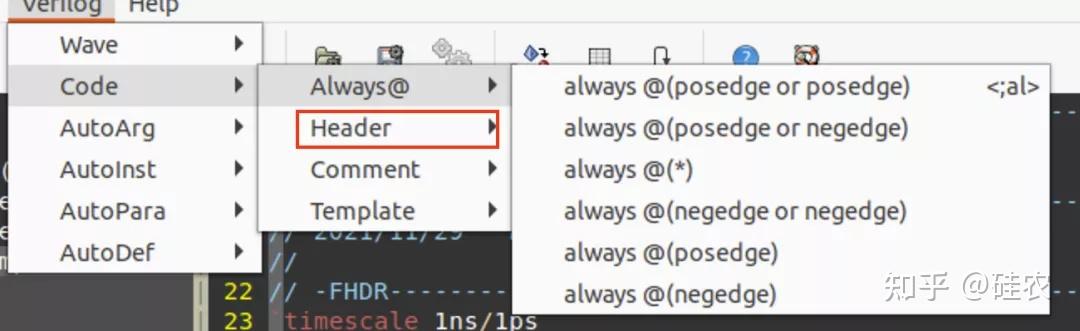

话说这个世界上只有三种编辑器,Vim , Emacs 和 其他编辑器,其中Vim被称作编辑器之神,Emacs被称其神的编辑器,当然,其他编辑器永远只能是其他编辑器。  博主是坚定的Vim党,gVim即gui Vim。Vim is the best text editor!  各大编辑器的学习曲线 各大编辑器的学习曲线对于编写Verilog的插件,本号之前也推荐过两个。第一个是源于Emacs的一个插件。 verilog-mode开发者网站在这里,更多内容去上网查询。https://www.veripool.org/wiki/verilog-mode但是这个插件的autodefine功能并不好用, 然后又被我找到了,vim官网上的一个插件,有好用的autodefine功能,写代码的时候可以完全不用在意reg和wire类型的定义,直接写assign和always块,最后autodefine一下就可以了。 https://www.vim.org/scripts/script.php?script_id=4067 但是这个插件不能跨文件夹。 所以博主我萌生了,自己写一个完全满足自己需求的,gVim插件!!!(此处有回音~)硅农:你那点python水平,心里没点B数吗?扎心了,但是,踏破铁鞋终于被我找到了一个,集合了上面那两个插件的所有优点的一个gVim插件。我愿称之为我见过的地表最强开源gVim编写Verilog插件。 autoinst自动例化支持任意跨文件夹例化  支持自动例化`ifdef随便怎么写,都给你例化进来   支持修改端口修改后保留不重刷支持Verilog1995和Verilog2001的端口描述语法支持例化模块端口修改后,注释哪些被修改,哪些新增  autodef自动定义 autodef自动定义直接写assign或者直接写always。然后完全可以自动定义wire或reg。尤其是做顶层的集成的时候,几千根wire连线,根本不是人做的。工作效率提高1000%  autopara自动para例化 autopara自动para例化支持替换变量名和自动例化数字两种方式。  autoarg自动定义端口 autoarg自动定义端口如果你喜欢1995的端口描述写法,直接帮你自动定义端口,我已经不写端口好多年。  支持显示RtlTree 支持显示RtlTree 上面说的已经是可以将编码效率提高1000%的最基本的,还有其他更多的功能。这里就不一一展示了。header、自动always块。代码中波形注释块等等。   安装使用 安装使用安装使用方法也很简单,直接放到vim安装目录的plugin路径中,如果有没有这个目录就新建一个。更重要的是,支持Windows、Linux、MacOs全平台呢。操作完全相同。  那么这怎么样才能得的到的呢?编写这个脚本的网友,已经全部开源,而且还在持续更新开发。你甚至可以自己在这个基础上再开发,做出符合自己的完全需求的Verilog插件。GitHub链接如下: https://github.com/HonkW93/automatic-verilog 他的个人网站有更加详细的介绍和使用方法。 https://blog.honk.wang/posts/AutoMatic/  最后 听我说,所有用gVim的都必须得用它,没用gVim的希望早点用。最后祝大家代码写的快,下班下得早!给我点赞,在看,分享三连!! |

【本文地址】

今日新闻 |

推荐新闻 |